### PE44951

### Evaluation Kit User's Manual

# Semi A Murata Company

#### Two-way Phase Shifter with Digital Step Attenuator

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

#### **Table of Contents**

| Introduction                                                                | 3   |

|-----------------------------------------------------------------------------|-----|

| PE44951 Functional Diagram                                                  |     |

| Evaluation Kit Overview                                                     |     |

| Evaluation Kit Contents and Requirements                                    | 4   |

| Hardware Requirements                                                       |     |

| Quick Start Guide                                                           | 5   |

| Evaluation Board Overview                                                   |     |

| USB Interface Dongle and Cables                                             | 6   |

| Connecting the Ribbon Cable                                                 | 8   |

| Operating the Hardware Evaluation Board Installing the Software             |     |

| Install the Keysight VEE Pro 9.33 RunTime software                          | 12  |

| Installing the FTDI DriversInstalling the Red Dongle Interface Files on the | )   |

| PC                                                                          |     |

| Using the Graphical User Interface                                          | .19 |

| Pin Information                                                             | 22  |

| Evaluation Board Schematic                                                  | 23  |

| Technical Resources                                                         | 24  |

#### Introduction

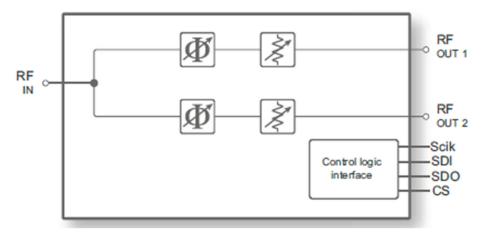

The PE44951 is a highly integrated two-way phase shifter with digitally controlled step attenuators for use across the 6.42–7.21 GHz frequency range. Each path is controlled through its respective Serial Peripheral Interface (SPI) control pins. The PE44951 is ideal for wireless infrastructure applications, such as massive multiple input, multiple output (mMIMO) macro and micro base stations, next generation 5G solutions, and small cell applications.

pSemi manufactured this phase shifter and attenuator using the pSemi UltraCMOS® process, a patented variation of silicon-on-insulator (SOI) technology on a sapphire substrate, which features high compactness, excellent isolation, and low insertion loss.

The PE44951 implements two RF paths with independent digital phase shift and digital step attenuation. Each phase shift value is set by the sum of an 8-bit beamformer phase buffer and an 8-bit AC phase buffer. The on-chip digital logic automatically computes these sums. An 8-bit register sets each attenuation value. The latch phase (LP) input pin provides precise control of the switching time of the phase shifters.

An SPI slave interface that operates at up to 50 MHz provides access to the beamformer, AC phase buffers, and the attenuator control registers.

#### PE44951 Functional Diagram

Figure 1. PE44951 Functional Diagram

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 3 of 24 www.psemi.com DOC-125948-1- (09/2025)

#### **Evaluation Kit Overview**

pSemi designed the PE44951 evaluation kit to ease your evaluation of the PE44951. You operate the evaluation board using a USB interface dongle and the associated pSemi software.

#### **Document Overview**

This *PE44951 Evaluation Kit (EVK) User's Manual* includes information about the hardware required to control and evaluate the functionality of the two-way phase shifter. This document also includes the pin configuration, schematic diagrams, cable connections, and software instructions.

#### **Evaluation Kit Contents and Requirements**

#### **EVK Contents**

Table 1 lists the hardware you need to evaluate the PE44951 two-way phase shifter.

Table 1. EVK Contents

| Quantity       | Description                       | Part Number |

|----------------|-----------------------------------|-------------|

| 1              | PE44951 evaluation board assembly | EK44951-01  |

| 1              | USB interface dongle              | PRT-50865   |

| 1 Ribbon cable |                                   | -           |

| 1              | USB cable                         | -           |

#### Hardware Requirements

To evaluate the performance of the evaluation board, you need the following equipment:

- Bench supply capable of providing 3.3V at 1A, with the current limit set to 100 mA

- Multimeter for checking V<sub>DD</sub>

- Vector network analyzer, ideally with three ports

**Warning**: The PE44951 two-way phase shifter EVK contains components that could be damaged by exposure to voltages higher than the maximum specified voltage, including voltages produced by electrostatic discharges. Handle the board in accordance with procedures for handling static-sensitive components. Avoid applying excessive voltages to the power supply terminals, or to signal inputs and outputs.

Before you connect the EVK to the source power supply, verify that the power supply is off. Connecting the EVK to a live power supply could induce failures.

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 4 of 24 www.psemi.com DOC-125948-1- (09/2025)

#### **Quick Start Guide**

pSemi designed the evaluation board to ease your evaluation of the PE44951 two-way phase shifter. This section guides you through the hardware configuration and the startup process.

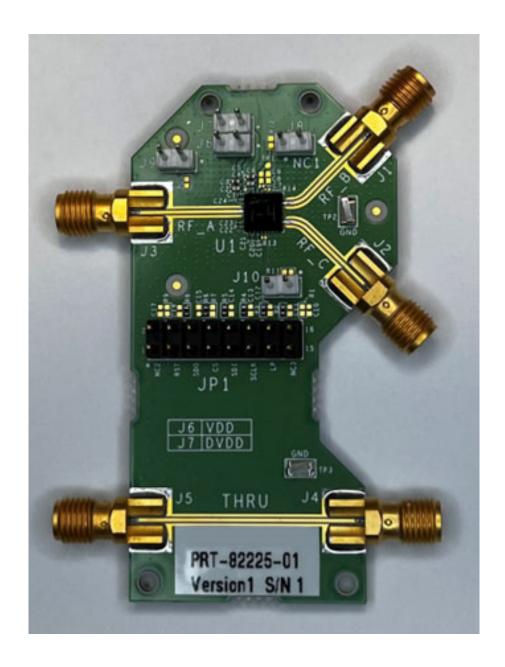

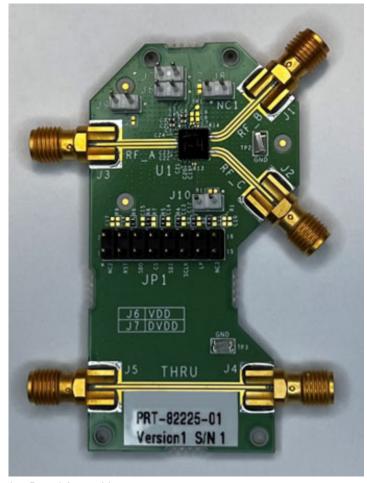

#### **Evaluation Board Overview**

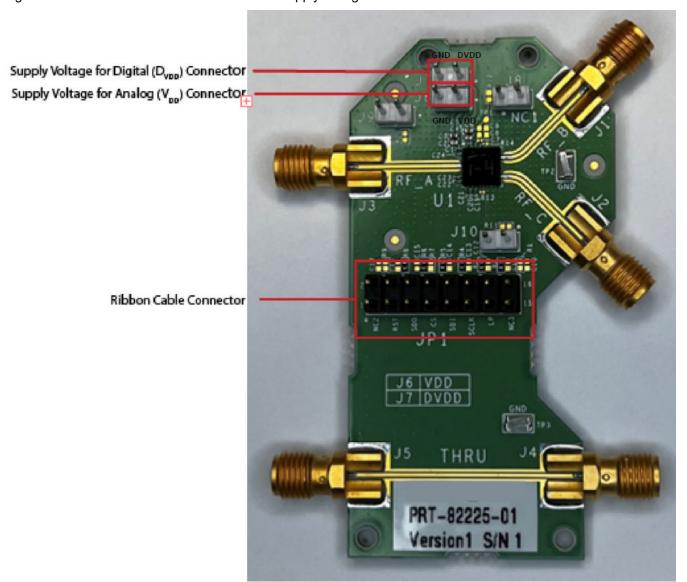

The evaluation board contains the following:

- J6 and J7 V<sub>DD</sub> input terminals

- JP1 connector for the interface dongle, which controls the SPI interface

- J3 common RF input

- J1 and J2 RF outputs

- Sense points and the power good (PGOOD) signal

Figure 2. PE44951 EVK Evaluation Board Assembly

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 5 of 24 www.psemi.com DOC-125948-1- (09/2025)

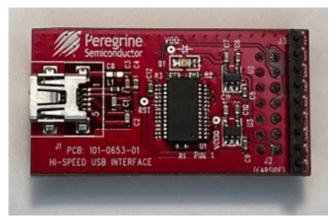

#### **USB Interface Dongle and Cables**

Figure 3 shows the PE44951 interface dongle (part number EK600000).

Figure 3. PE44951 Interface Dongle

Figure 4 shows the PE44951 evaluation board ribbon cable.

Figure 4. PE44951 EVK Ribbon Cable

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 6 of 24 www.psemi.com DOC-125948-1- (09/2025)

Figure 5 shows the PE44951 evaluation board USB cable.

Figure 5. PE44951 EVK USB Cable

Figure 6 shows the PE44951 evaluation board supply voltage and ribbon connectors.

Figure 6. PE44951 Evaluation Board Supply Voltage and Ribbon Cable Connectors

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 7 of 24 www.psemi.com DOC-125948-1- (09/2025)

#### Connecting the Ribbon Cable

- 1. Connect the external power supplies to the V<sub>DD</sub> connector (J6) and the D<sub>VDD</sub> connector (J7).

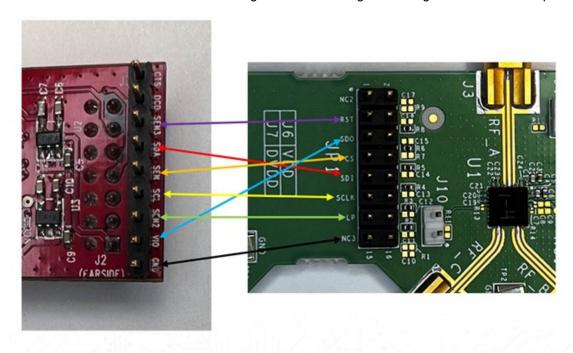

- 2. Connect the ribbon cable to JP1 on the evaluation board, as shown in Figure 7.

Note that one orange/yellow pair of wires and one brown/red pair of wires are not connected to JP1.

Figure 7. Connect the External Power Supplies and Ribbon Cable to the PE44951 Evaluation Board

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 8 of 24 www.psemi.com DOC-125948-1- (09/2025)

3. Connect the ribbon cable to the interface dongle as shown in Figure 8 using the connection map in Table 2.

Figure 8. Connect the Ribbon Cable to the Evaluation Board

Table 2. PE44951 Ribbon Cable Connections

| Interface Dongle Connection | Evaluation Board Connection |

|-----------------------------|-----------------------------|

| GND                         | NC3                         |

| SCL                         | SCLK                        |

| SDA                         | SDI                         |

| SEN                         | CS                          |

| VIO                         | SDO                         |

| SEN2                        | LP                          |

| SEN3                        | RST                         |

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 9 of 24 www.psemi.com DOC-125948-1- (09/2025)

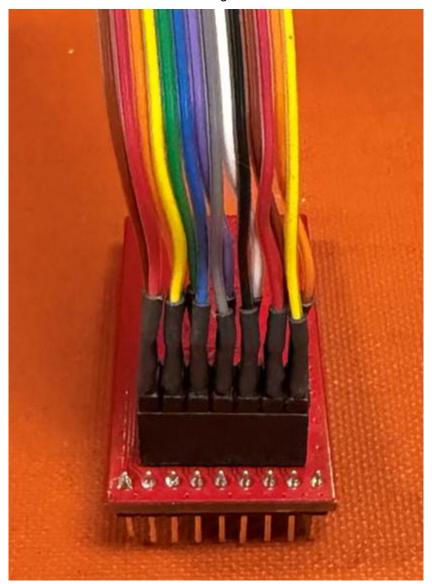

Figure 9 shows the ribbon cable connected to the red dongle.

Figure 9. Ribbon Connected to the Red Dongle

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 10 of 24 www.psemi.com DOC-125948-1- (09/2025)

#### Operating the Hardware Evaluation Board

- 1. Install the jumper on JP8, JP9, and JP10.

- 2. Use JP6 to provide the  $V_{DD}$  to the part.

- 3. Use JP7 to provide  $D_{VDD}$  to the part. For the range of voltages that can be applied to  $V_{DD}$  and  $D_{VDD}$ , see Table 3.

- 4. Plug in the USB interface board.

- 5. To calibrate the board trace loss and phase, use the THRU trace between connectors J4 and J5. This THRU calibration is sufficient for the initial measurements.

- To drive the PE44951 using your own SPI setup, see the PE44951 Data Sheet for details on the SPI word structure, register addresses, and phase summation feature. To access the PE44951 Data Sheet, see the pSemi website.

Table 3. Recommended Operating Conditions

| Parameter                                                                                         | Min        | Тур | Max          | Unit     |

|---------------------------------------------------------------------------------------------------|------------|-----|--------------|----------|

| Supply voltage for analog, VDD                                                                    | 3.15       | 3.3 | 3.45         | V        |

| Supply voltage for digital, D <sub>VDD</sub>                                                      | 1.7        | _   | 3.45         | V        |

| Supply current                                                                                    | -          | -   | 1            | mA       |

| Digital input high                                                                                | 1.17       | -   | Dvdd         | V        |

| Digital input low                                                                                 | 0          | _   | 0.63         | V        |

| Operating temperature range:  @ Package case, full functionality @ Package case, full performance | -40<br>-33 | _   | +115<br>+115 | ů<br>C   |

| D <sub>VDD</sub> supply current <sup>(1)</sup> Standby Operation                                  | -          | _   | TBD<br>TBD   | μA<br>mA |

| Digital output high level, I <sub>OUT</sub> = 2 mA                                                | TBD        | -   | _            | _        |

| Digital output low level, I <sub>OUT</sub> = 2 mA                                                 | -          | -   | TBD          | _        |

| RST pulse width, RST = low (active)                                                               | 10         | _   | _            | ns       |

| LP pulse width, high or low                                                                       | 4          | _   | _            | ns       |

| LP lead/lag SPI command <sup>(2)</sup>                                                            | 20         | _   | _            | ns       |

#### Notes:

- 1) RST = CD = high, SCLK = SDI = LP = low, 50-MHz SCLK frequency, CL = 34 pF at the SDO pin.

- 2) LP low-to-high or high-to-low before/after the SPI command 20 ns.

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 11 of 24 www.psemi.com DOC-125948-1- (09/2025)

#### Installing the Software

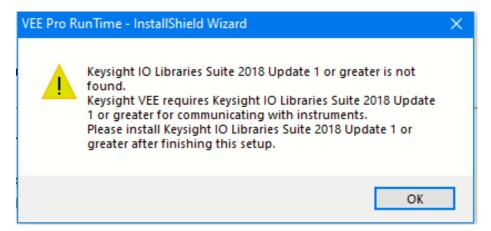

Install the Keysight VEE Pro 9.33 RunTime software

- Download the Keysight VEE software from the <u>Keysight Technologies website</u>.

- To start the software installation, run the downloaded Keysight\_VEE\_Pro\_9.33\_RunTime\_setup.exe file.

The InstallShield Wizard displays.

10. Select **OK**. The Welcome screen displays.

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 12 of 24 www.psemi.com DOC-125948-1- (09/2025)

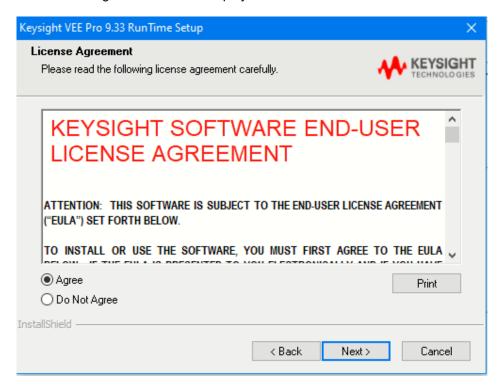

11. Select Next. The License Agreement screen displays.

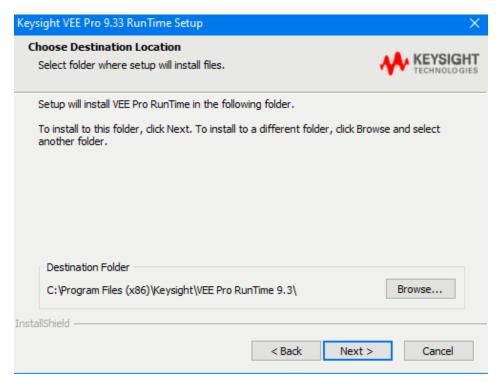

12. Select Agree, then select Next. The Choose Destination Location screen displays.

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 13 of 24 www.psemi.com DOC-125948-1- (09/2025)

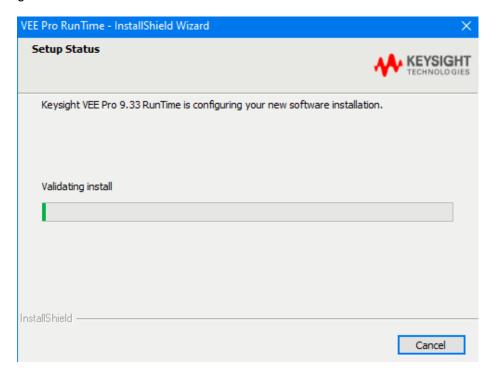

13. Select the preferred destination folder, then select **Next**. The Setup Status screen displays, and the installation begins.

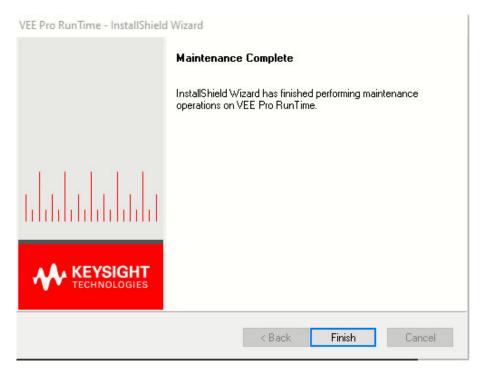

14. After the installation is completed, the Maintenance Complete screen displays.

15. To complete the VEE Pro RunTime software installation, select Finish.

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 14 of 24 www.psemi.com DOC-125948-1- (09/2025)

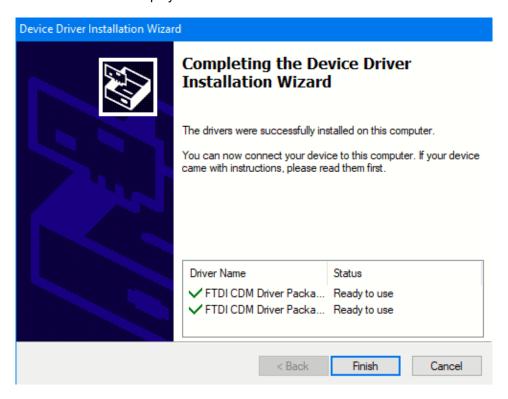

#### Installing the FTDI Drivers

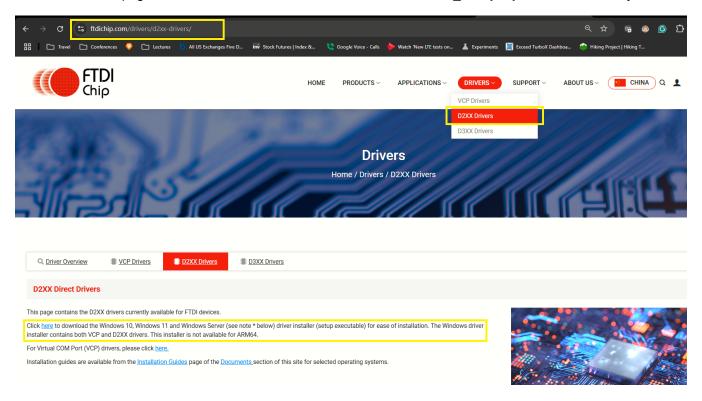

- 1. Download the FTDI driver from the FTDI website at https://ftdichip.com/drivers/d2xx-drivers/.

- 2. From the *Drivers* menu of the website, select **D2XX Drivers**, then scroll down to the D2XX Direct Drivers section of the page and select the **Select here** link. The **CDM2123620\_Setup.zip** file downloads to your PC.

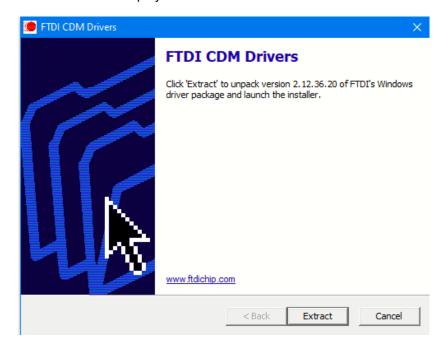

3. In the Downloads folder, extract the **CDM2123620\_Setup.zip** file, then select the **CDM2123620\_Setup.exe** file. The FTDI CDM Drivers screen displays.

4.

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 15 of 24 www.psemi.com DOC-125948-1- (09/2025)

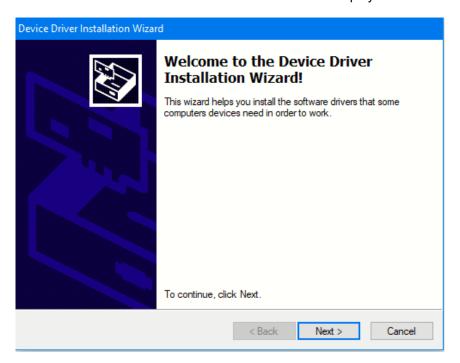

5. Select Extract. The Device Drive Installation Wizard Welcome screen displays.

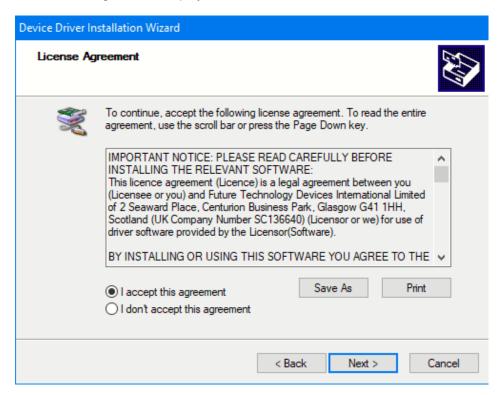

6. Select Next. The License Agreement displays.

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 16 of 24 www.psemi.com DOC-125948-1- (09/2025)

7. Select **I accept this agreement**, then select **Next**. The software installs the device drivers, and the Device Drive Installation Wizard screen displays.

8. To complete the device driver installation, select **Finish**.

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 17 of 24 www.psemi.com DOC-125948-1- (09/2025)

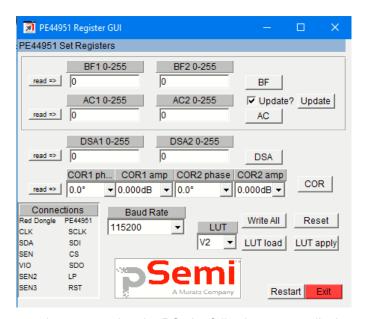

#### Installing the Red Dongle Interface Files on the PC

- 1. Download the **PE44951 folder** from the shared folder present at the FTP build.

- 2. Navigate to \\\StandaloneUtilities\\PE44951\\PE44951\_SetRegisters.vxe,\) and create a desktop shortcut for the PE44951 SetRegisters.exe file.

- 3. Connect the red dongle to the PC using the USB cable provided, then wait for one minute.

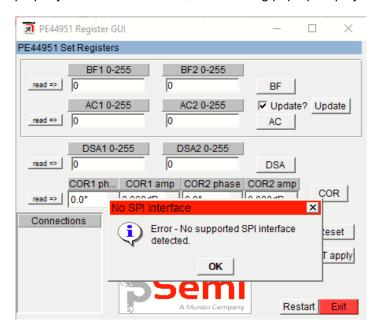

- 4. Select **PE44951\_SetRegisters.vxe**. If the red dongle is properly connected to the PC, the PE44951 Register Gui screen displays, and the *Connections* section of the screen displays all the connections.

5. If the red dongle is not properly connected to the PC, the following pop-up displays.

6. If the red dongle is still connected to the PC and the error message still displays, select **OK** and then select **Restart**.

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 18 of 24 www.psemi.com DOC-125948-1- (09/2025)

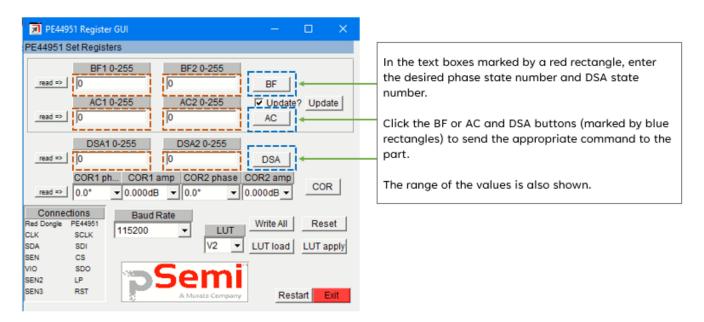

#### Using the Graphical User Interface

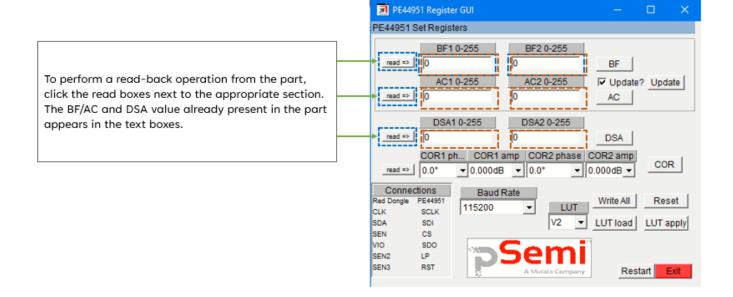

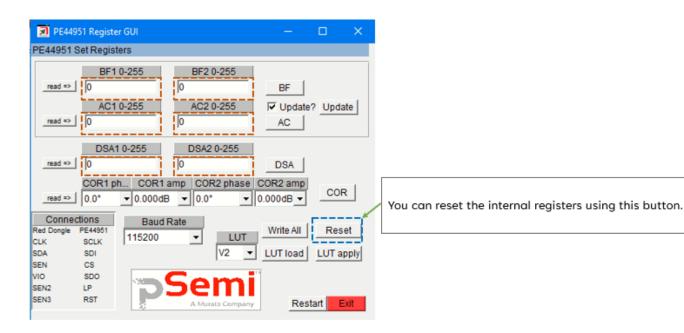

For detailed information about the beamformer (BF) phase buffer, amplitude control (AC) phase buffer, and digital step attenuation (DSA) settings, see the "Detailed Description" section of the *PE44951 Data Sheet*.

In the screen images that follow, select the **Update?** check box and the **Update** button to latch in the phase (the LP line goes high). The phase values are not activated until you select the **Update** button, or you select the **Update?** check box, which latches the values automatically. Do *not* select the **COR** button.

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 19 of 24 www.psemi.com DOC-125948-1- (09/2025)

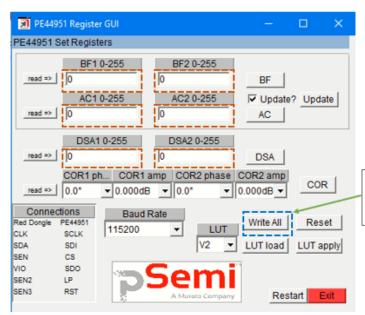

Instead of selecting each BF/AC and DSA individually, you can write all the data at once to the part.

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 20 of 24 www.psemi.com DOC-125948-1- (09/2025)

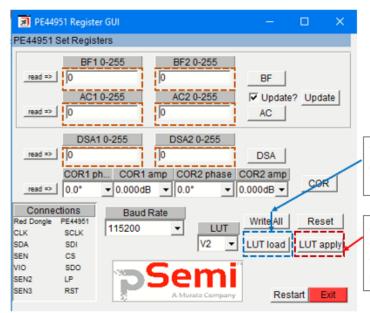

The lookup tables (LUT) reside in the same location as the installer for the PE44951 Register GUI: Location: \\StandaloneUtilities\PE44951\LUT\

Click **LUT apply** to instantiate the lookup table. After the lookup tables are applied, the phase steps and the amplitude steps become more accurate for the part.

Page 21 of 24 www.psemi.com DOC-125948-1- (09/2025)

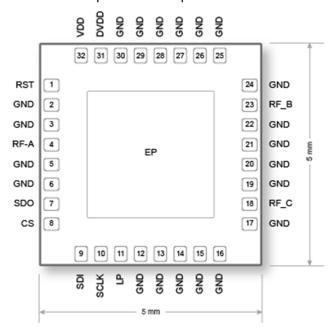

#### Pin Information

Figure 10 shows the PE44951 pin map for the 32-lead  $5 \times 5 \times 0.7$  mm FCLGA package, and Table 4 lists the description for each pin.

Figure 10. Pin Configuration (Top View)

Table 4. PE44951 Pin Descriptions

| Pin No.                                                                                          | Pin Name | Description                |  |

|--------------------------------------------------------------------------------------------------|----------|----------------------------|--|

| -                                                                                                | EP       | Exposed ground pad         |  |

| 1                                                                                                | RST      | Reset (active low)         |  |

| 2, 3, 5, 6, 12,<br>13, 14, 15,<br>16, 17, 19,<br>20, 21, 22,<br>24, 25, 26,<br>27, 28, 29,<br>30 | GND      | Ground                     |  |

| 4                                                                                                | RF_A     | RF input                   |  |

| 7                                                                                                | SDO      | Serial data output         |  |

| 8                                                                                                | CS       | Chip select (active low)   |  |

| 9                                                                                                | SDI      | Serial data input          |  |

| 10                                                                                               | SCLK     | Serial data block          |  |

| 11                                                                                               | LP       | Latch phase (active high)  |  |

| 18                                                                                               | RF_C     | RF output 2                |  |

| 23                                                                                               | RF_B     | RF output 1                |  |

| 31                                                                                               | DVDD     | Supply voltage for digital |  |

| 32                                                                                               | VDD      | Supply voltage for analog  |  |

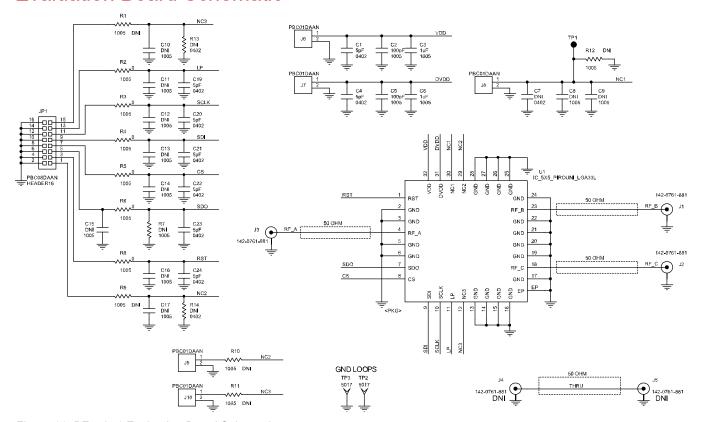

#### **Evaluation Board Schematic**

Figure 11. PE44951 Evaluation Board Schematic

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Page 23 of 24 www.psemi.com DOC-125948-1 – (09/2025)

#### **Technical Resources**

Additional technical resources are available for download in the Products section at <a href="www.psemi.com">www.psemi.com</a>. These include the product specification datasheet, S-parameters, zip file, evaluation kit schematic, bill of materials, material declaration form, and PC-compatible software file.

Trademarks are subject to trademark claims.

#### Sales Contact

For additional information, contact Sales at sales@psemi.com.

#### Disclaimers

The information in this document is believed to be reliable. However, pSemi assumes no liability for the use of this information. Use shall be entirely at the user's own risk. No patent rights or licenses to any circuits described in this document are implied or granted to any third party. pSemi's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the pSemi product could create a situation in which personal injury or death might occur. pSemi assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

#### **Patent Statement**

pSemi products are protected under one or more of the following U.S. patents: patents.psemi.com

#### Copyright and Trademarks

©2025, pSemi Corporation. All rights reserved. The Peregrine Semiconductor name, Peregrine Semiconductor logo and UltraCMOS are registered trademarks and the pSemi name, pSemi logo, HaRP and DuNE are trademarks of pSemi Corporation in the U.S. and other countries.

#### Corporate Headquarters

9369 Carroll Park Drive, San Diego, CA, 92121 USA +1-858-731-9400

©2025, pSemi Corporation. All rights reserved. • Headquarters: 9369 Carroll Park Drive, San Diego, CA, 92121

Evaluation Kit User's Manual www.psemi.com DOC-125948-1 - (09/2025)